Home > On-Demand Archives > Talks >

Let’s Assume the System is Synchronized

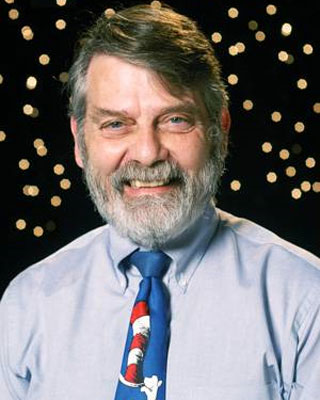

fred harris - Watch Now - DSP Online Conference 2025 - Duration: 02:12:37

It is amazing how many papers on radio systems contain a version of the sentence “Let’s assume the system is synchronized.” Alright, let’s assume the system is synchronized. But I have a few questions: Who did it? How did they do it? Who will do it in the next decades as many of us retire from the field? An important one is: where are they acquiring the skills required to negotiate and navigate future physical layers?

This brings us to the question of “What do we mean by synchronize”? Its etymology starts with Chronos, the ancient Greek Immortal Being personified in the modern age as Father Time. We thus form synchronize from the Greek prefix syn, meaning “together with,” and chronos which we interpret as “time”.

With the industrial revolution and the rise of high-speed railroads came the need to synchronize clocks in adjacent towns to maintain timetables and prevent accidents. Today, the higher-speed transport of communication signals places an even greater premium on time measurement and alignment of remote clocks and oscillators.

When discussing the importance of synchronization in my modem design class, I remind students that Momma’s middle name is synchronizer! If the radio is not synchronized, no other system can operate—

- Not the matched filters

- Not the equalizer

- Not the detectors

- Not the error correcting codes

- Not the decryption

- Not the source decoding

At the waveform level, synchronization entails the frequency and phase alignment of remote oscillators for carrier acquisition and tracking, symbol timing, and chip alignment in spread spectrum systems.

What have we missed by assuming the system is synchronized? We’ve skipped a challenging and fascinating part of the process: estimating unknown parameters of a known signal in noise. We’ve replaced the task of processing a noisy waveform with processing a binary stream, and we’ve skipped making Momma happy!

Digital Signal Processing is now standard in modulators and demodulators of modern systems. These require acquiring carrier and clock from signals where neither is explicitly present. Synchronization info must be extracted from:

- Implicit side information in the modulated signal

- Explicit side information in pilot signals

Many ad-hoc analog synchronization methods predate optimal techniques. As DSP emerged, these analog schemes were often digitized and reused. But returning to first principles in DSP can offer performance gains.

In this presentation, we’ll review:

- Receiver structures and parameters to estimate

- Eye and constellation diagrams

- Phase-locked loops and their digital counterparts

- Timing and carrier recovery methods (with and without data decisions)

- Real-world synchronization in modern systems

MATLAB demos will illustrate key ideas. We’ll also highlight historical and modern synchronization techniques from the Digital Communications: Fundamentals and Applications text by Bernie Sklar and Fred harris. The tutorial’s goal is to equip DSP radio designers with modern synchronization methods made possible by DSP maturity—enhancing performance, reducing cost, and improving design satisfaction.

This guide was created with the help of AI, based on the presentation's transcript. Its goal is to give you useful context and background so you can get the most out of the session.

What this presentation is about and why it matters

Fred Harris takes on a deceptively short sentence that appears in many papers and designs: “Let’s assume the system is synchronized.” This talk flips that assumption into a practical engineering problem: how do you acquire and track carrier frequency, carrier phase, and symbol timing in real, noisy, band-limited links when the transmitter does not send an explicit reference? The presentation explains why synchronization is the heart of any modem — if clocks and carriers are not aligned, matched filters, equalizers, detectors, decoders and even encryption will fail — and it shows the DSP-era tools that make robust synchronization possible.

Who will benefit the most from this presentation

- Graduate students and advanced undergraduates studying digital communications and DSP who want a practical view of synchronization problems.

- RF and baseband engineers implementing or debugging modem receivers, software-defined radios (SDRs), and digital front ends.

- System designers choosing synchronization architectures (pilot vs decision-directed, PLL vs FLL, analog vs digital).

- Educators looking for historical perspective and MATLAB examples to illustrate carrier/timing recovery concepts.

What you need to know

The talk assumes familiarity with basic digital-communications building blocks; reviewing the items below will make the material easier to follow.

- Complex baseband and I/Q representation — symbols are points in the complex plane (I and Q). A carrier rotation is a multiplication by e^{j\theta(t)}; using the complex baseband simplifies carrier and timing processing.

- Simple phase model — the instantaneous phase is typically represented as \(\theta(t)=\omega_0 t + \theta_0\), with frequency \(\omega_0\) and phase offset \(\theta_0\). Frequency is the derivative \(d\theta/dt\).

- Matched filter and sampling — the receiver uses a matched filter (time-reversed conjugate of the transmit pulse) to maximize SNR; timing recovery finds the sampling instant at the matched-filter peak.

- Correlation and error formation — minimizing mean-squared error between received waveform and a local estimate leads to maximizing a correlator term: \(\int (r-\hat s)^2 = \int r^2 + \int \hat s^2 - 2\int r\hat s\). The phase/ timing loop uses derivatives of such correlators as error signals.

- Phase-locked loops (PLLs) and Type-II loops — proportional-plus-integral control keeps frequency and phase errors driven to zero. In sampled systems the bilinear map (Tustin) is often used to translate analog loop designs into digital gains.

- Detectors: decision-directed vs non-decision — decision-directed detectors use symbol decisions (hard or soft) to form phase/timing errors; soft nonlinearities (e.g., tanh-scaled decisions) are MMSE-like and are robust across SNR regimes.

- Timing recovery methods — derivative-based (matched-filter derivative), Gardner (midpoint/half-symbol sampler), and Mueller & Müller approaches, plus the polyphase interpolator implementation for fractional delay.

- Costas loop and suppressed-carrier cases — when the carrier is suppressed you use nonlinear products (multipliers or sign-products) to generate a usable carrier component; Costas-like architectures implement this for M-PSK/QPSK.

- Digital synthesis and quantization issues — direct digital synthesizers (DDS) use truncated phase accumulators and lookup tables; dithering or sigma–delta feedback shapes/address-quantization error and suppresses spurs.

- Frequency-locked loops (FLLs) and band-edge detectors — if the constellation is rotating due to frequency offset, an FLL or band-edge-energy difference detector is used to estimate and remove the frequency error before PLL locking.

Glossary

- Synchronization — aligning remote oscillators in frequency and phase and aligning sampling instants (symbol timing) between transmitter and receiver.

- Carrier recovery — estimating and tracking the carrier frequency/phase to undo rotation of the constellation.

- Timing recovery — finding the correct sampling instants (matched-filter peak) so symbol decisions are optimal.

- Matched filter — the receive filter that maximizes SNR for known pulse shape (time-reversed conjugate of transmit pulse).

- PLL (Phase-Locked Loop) — a feedback system that locks a local oscillator to the phase/frequency of an incoming tone or phasor.

- FLL (Frequency-Locked Loop) — extracts frequency error (often via band-edge or correlator methods) to remove rotation before PLL.

- Costas loop — a popular carrier recovery loop for suppressed-carrier PSK/QPSK that uses products of I and Q to form phase error.

- DDS (Direct Digital Synthesizer) — a digital phase accumulator + lookup table that generates sinusoids in DSP implementations.

- Polyphase interpolator — implements fractional delay by selecting one of many phase-shifted filter outputs (efficient fractional timing control).

- Decision-directed / soft decision — using symbol estimates (hard or scaled soft values like tanh) to form phase/timing error signals, with soft decisions improving low-SNR robustness.

Final note

Fred Harris packs historical perspective, practical design rules, and DSP-era refinements into a single, lively tutorial. Expect clear intuition (analog stories and car/“gas pedal” metaphors), worked MATLAB demos, and useful implementation tips — from Costas loops to sigma–delta noise shaping and polyphase timing — that will immediately help you design or diagnose modern receivers. If you care about making “Momma’s synchronizer” happy, this talk is a friendly and authoritative roadmap into the mechanics of synchronization.

Offset QPOSK has an interesting problem. The timing and phase PLLs have to be nested, they don't work well if the run as two different loops. This may be part of the problem. I just tried looking for my code, will have to spend more time

can you post the code for the presentation. I'm looking for the band edge filter examples.

Is the band edge FLL supposed to work also for Offset QPSK? While my implementation works fine for vanilla QPSK, I couldn't make it work reliably for OQPSK.